#### **Introduction**

The goal of this project was to develop a remote locator device that is used to find lost items by sending an RF signal to small remote units connected to various items in the home, such as keys, TV remotes, etc. When an item is lost, the user scrolls through a LCD screen located on the base unit. The name of the lost item is found in a list of saved names and is selected for location. The remote unit attached to the desired item receives the RF transmitted digital ID code from the base unit and produces an audible alert tone to allow the user to locate the item. Each additional remote unit also receives the signal, but they do not produce the audible alert. The user is able to turn the alert off on the portable device or use a button on the base unit.

#### Significance of the Project

This product will benefit those people that have multiple items in their home that tend to get lost on a regular basis. The user will no longer have to spend time searching their home for remotes, keys, or other items that are used and misplaced regularly. The target audience for this device will be homeowners or renters between the ages of 25 and 55 that own TVs, VCRs, stereos, and/or a car. These people will have multiple remote controls and keys that may be misplaced on a regular basis. Consumers that have enough money to purchase these items will have enough money to purchase these items will have enough money to purchase this device. This product will end the frustration of having to search one's home repeatedly for lost items.

#### **System Description**

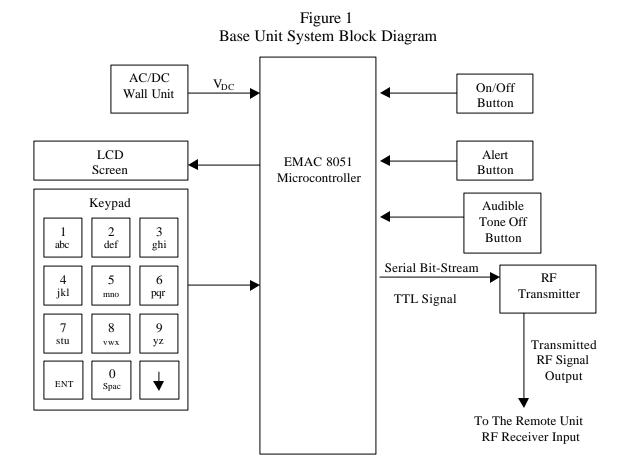

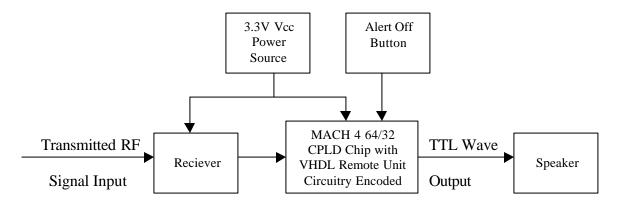

This project was divided into two major components, the base unit and the remote unit. The base unit was microcontroller based, utilizing a LCD and a keypad. A user menu is displayed on the LCD and allows three different modes of operation: save mode, alert mode, and load mode. The base unit is controlled by a user input from the keypad and outputs a packed serial bit-stream through a RF transmitter. This is shown in figure 1. The remote unit was implemented on a CPLD development board using VHDL code. The transmitted packed serial bit-stream acts as the input to the remote unit. The remote unit produces an audible alert tone through the speaker so that it can be located.

Figure 2 Remote Unit Top Level Block Diagram

### **Modes of Operation**

- Save Mode: This mode is used to save the name of each item to be located and to assign each item to its remote device. The names are entered into the list using the keypad. When the names of the items are saved into the menu, the user is then able to scroll through the list of names and locate the desired item when in the alert mode.

- Alert Mode: The keypad is used to scroll down the list of saved items in order to find the desired item. The user can then select the desired item and press the alert button to transmit the RF signal to each remote unit. Upon receiving, the signal is delivered to a comparator circuit where each remote unit can compare the signal to its own ID number. When the correct remote receives the signal, it sounds the alert on the remote so that the item can be found.

- Load Mode: The load mode is used when the user wants to add or replace a remote device in the system. The additional remotes each have a preset code that is entered into the base unit and stored so that the base unit knows what signal to send in order to activate the remote.

### **Base Unit Inputs**

| nit. |

|------|

| ni   |

- Keypad: The keypad is used to enter the names of the items, select the items, and store the ID numbers of the locators. Ideally, the keypad would be a twelve button alpha numeric keypad that interfaces with a microcontroller and consists of a back button, an enter button, a scrolling button, all the letters of the alphabet, and the numbers 0-9.

- On/Off button: This button turns the power to the base unit on and off.

Alert Button: This button is pressed in order to send the signal to the locator devices when it is desired to locate an item.

Off Button: This button allows the user to turn the audible alert tone off from the base unit. The alert tone is turned off by sending a reset signal to each remote unit. The remote units will then automatically go into an idle state.

#### **Base Unit Outputs**

Audible Tone

- LCD: The display outputs the main menu and the modes of operation on the display screen.

- Microcontroller: When the alert button is pressed, the microprocessor in the base unit outputs a UART compatible packed bit-stream to the

transmitter. The structure of the bit-stream is described in the UART circuitry section on page 5.

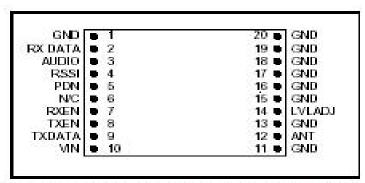

RF Transmitter: The packed bit-stream transmits to all of the remote units. The transmitter being used is the LINX Technologies SC series RF transceiver. (Appendix B shows the data sheet and pin configuration for the transceiver)

### **Remote Unit Inputs**

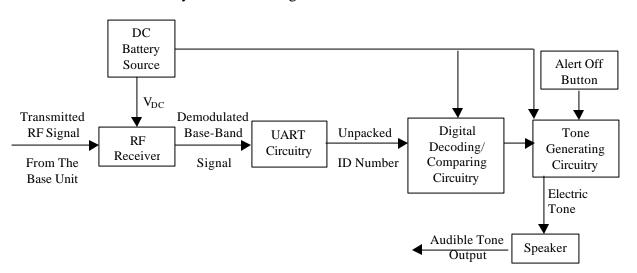

Figure 3 Subsystem Block Diagram Of The Remote Unit

Vcc: A small battery is used to power each remote unit and all of their components.

- Receiver: The transmitted RF signal is then received from the base unit and demodulated. The receiver then outputs the demodulated baseband signal to the UART circuitry. The receiver used is the LINX Technologies SC series RF transceiver. (Appendix B shows the data sheet and pin configurations for the transceiver)

- Off Button When pressed, this button turns the audible alert tone off by resetting the remote unit latch circuitry.

- Remote Signal: Each remote unit receives the RF signal transmitted from the base unit, through the RF receiver, every time the alert button is pressed.

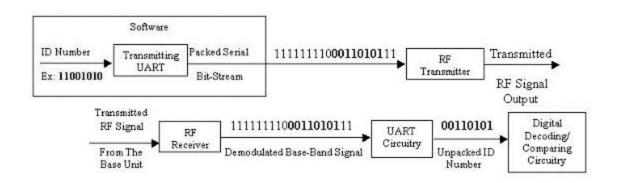

UART Circuitry: The UART is used to separate the ID number from the packed serial bit-stream transmitted from the base unit. The UART receives the demodulated base-band signal from the receiver and then unpacks the ID code from the serial bit-stream received by determining the beginning and the end of the transmitted signal. The UART then removes the start and stop bits that were added to the ID number prior to transmission and triggers the compare circuitry to begin comparing its preset ID code to the code in the shift register circuitry.

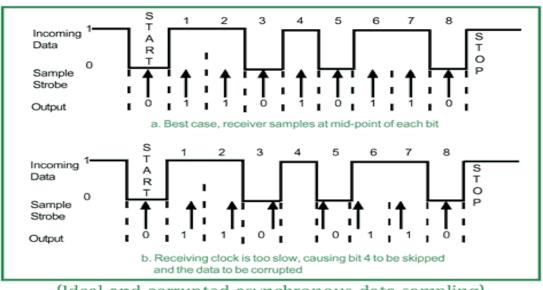

In order to determine what ID code has been transmitted, the UART determines the start and stop bits of the remote signal. An initial stream of high bits indicates that the remote signal is being received. The UART then waits for the first low bit to be received. This initial low bit is also known as the start bit of the signal. This bit is how the UART recognizes the start of the input signal. After the UART receives the start bit, it knows that the next eight bits will be data bits that represent the ID number and the last bit is the stop bit. The stop bit is always high and it signals the end of the transmitted signal. The UART then outputs a high bit to the shift register/compare circuitry. At this time, the values stored in the shift register are compared to the preset ID code of the remote unit. Figure 4 is a representation of how the UART will unpack the ID number.

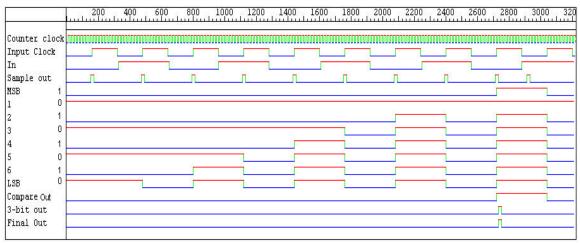

Figure 4 UART Signal Packing and Unpacking

When the initial high bits received by the UART first drop low, a sample is taken halfway through the pulse in order to determine if the negative transition is due to noise or the start bit. If the pulse sampled is high again, the UART determines that the negagive transition was due to noise. If the pulse is still low when it is sampled, the circuitry assumes that the start bit has been received. After determining the start bit, the UART acquires samples halfway through each of the eight data bits. This is done by having the UART clock run a standard 16 times faster than the input signal rate. Every time the UART clock counts to 16, it will be able to sample the next bit. Sampling halfway through the pulses at 16 times the receiver clock keeps the UART from accidentally missing a pulse while unpacking the ID number. After the UART samples the eight data bits, it samples the last bit to make sure it is a high stop bit. If the UART

counts eight bits and then the ninth bit is not a high bit, then it will assume that a mistake has occurred and will begin waiting for the next negative transition in the signal. The unpacked ID number is then sent to the digital decoding and compare circuitry. Quatech uses Figure 5 compare the ideal asynchronous data sampling used to unpack the ID number to non-ideal data sampling that has corrupted the signal. In addition, figure 5 shows how sampling 16 times the speed of the input clock benefits the system. By sampling at this rate, the UART is able to check each bit in the approximate middle of the pulse as shown in the top of the figure. The bottom half of figure 5 shows what would happen if the UART did not sample half way through the pulse. Eventually the UART may accidentally miss a bit and corrupt the data.

Figure 5 Asynchronous Signal Sampling

(Ideal and corrupted asynchronous data sampling)

### Digital Decoding/

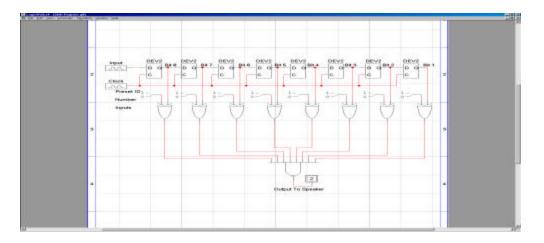

Comparing Circuitry: The purpose of this circuitry is to determine the ID code that has been transmitted and to compare this code to the preset code of the remote unit. Each bit of the ID number is stored in a different flipflop of an eight-bit shift register in order to decode and determine the ID number. The output of each flip-flop will be compared to the preset number for each remote unit. If each flip-flop output matches the preset number, the circuitry produces a high output to the tone generating circuitry. If the ID codes do not match, the output of the decoding logic remains low. If a remote unit receives the reset code from the base unit, it will reset the tone generating circuitry. Figure 6 shows the schematic for an eight-bit Shift register with compare circuitry.

Figure 6 8-Bit Shift Register With Compare

### Tone Generating Circuitry:

When the correct ID has been received and compared correctly, this circuitry generates a TTL wave output to the speaker.

The tone generating circuitry consists of a latch and a frequency divider. After the UART has determined the start bit, stop bit, the eight data bits, and the compare circuitry has compared correctly, the latch produces a high output to the frequency divider. The frequency divider divides the 2kHz UART clock four times in order to produce a 500Hz TTL wave. A 500Hz pulse was needed in order for the speaker to produce the desired tone. The circuitry will produce this wave until the latch is reset by the audible tone off button on the base or remote unit.

### **Remote Unit Output**

Speaker: The speaker on the locator device produces an audible alert tone when it receives a TTL frequency wave input from the tone generating circuitry.

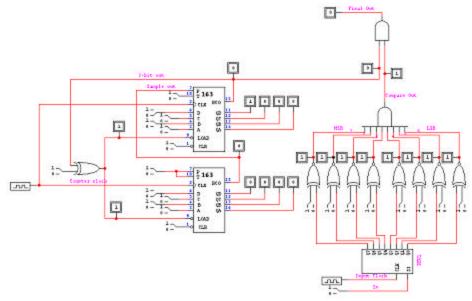

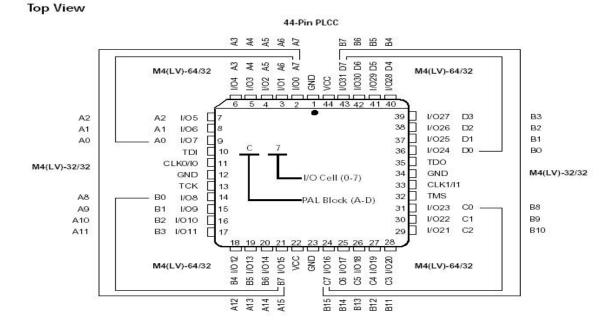

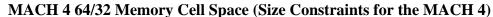

Figure 3 shows the subsystem block diagram for the remote units. Figure 7 shows the basic hardware schematic for the remote units with the output shown in figure 8. The VHDL code for the remote unit is shown in Appendix A-II. The CPLD pin assignments, as well as the CPLD memory cell limitations, are shown in Appendix B.

Figure 7 Hardware Schematic Of The Remote Units

Figure 8 Digital Decoding/Compare Circuitry Hardware Simulation Output

The operation of the remote units is shown in figure 8 above. The circuitry is activated when the first start bit causes a negative transition in the input bit-stream. The UART circuitry counts each bit as they are shifted through the shift register. When the ninth bit is counted, the UART samples it to make sure that it is a high bit. If the ninth bit is a high bit, the UART assumes that the stop bit has been reached and allows the compare circuitry to asses whether or not the correct ID code has been received. IF the

input matches the preset ID, the compare circuitry outputs high. This final output leads to the latching circuitry that produces the continuous TTL output wave to the speaker.

### <u>Software</u>

### Base Unit

Overall, seven different assembly code modules control the base unit. These modules are titled "setup", "main", "LCD", "keypad", "top menu", "serial port", and "alert menu". The functions of each module are shown in the base unit module section below. These modules are implemented using the Micropac 80515 (EMAC) microcontroller. The different components of the base unit are described in the base unit section. The operation by mode section describes the intended flow of each mode of operation. Appendix A-I shows the assembly code written.

### **Base Unit Modules**

- Setup: Initializes the LCD, Keypad, and serial port.

- Main: Calls the different modules.

- LCD: Includes all LCD output code and displays using the LCD screen.

- Keypad: Recognizes what button is pressed on the keypad. Used to select Modes, Items, and to alert.

- Serial: Has all the serial port definitions and transmits the desired ID code.

- Alert Menu: Displays the names of all the saved items. Allows the user to scroll through the names in order to select an item and alerts the item. The user can also chose the back button to go back to the main menu.

Top Menu: Utilizes LCD code to display the Main menu as shown below. (1) ALERT (2) SAVE

#### (3) LOAD

The written assembly code of all of these modules is shown in Appendix A-I.

### **Operation By Mode**

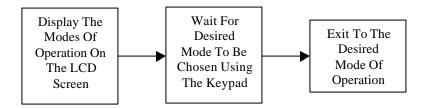

- Main Menu: The main menu allows the user to choose which mode of operation to use. This menu is displayed on the LCD and the user selects the desired mode by pressing a key. Figure 9 show the software flow chart for the main menu.

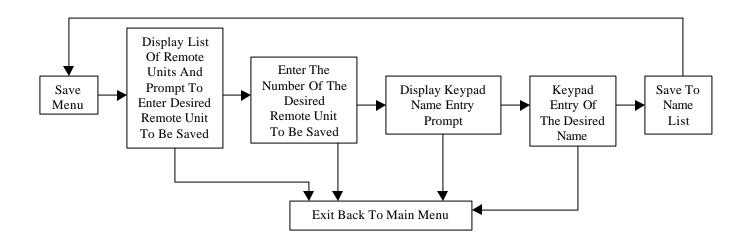

- Save Mode: The user is prompted by the LCD to select which remote unit to name. The user then utilizes the keypad to select the desired remote unit. Next,

the name of the remote unit is entered into the system using the keypad. The microcontroller then saves the entered name in a module and the LCD goes back to displaying the main menu. The remote unit is not used during this mode of operation. Figure 10 shows the software flow chart for the Save Mode.

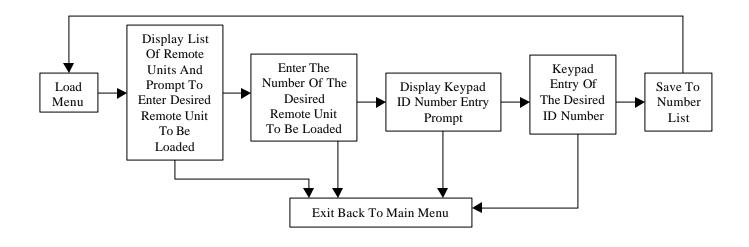

- Load Mode: The LCD prompts the user to choose which remote unit is being added or replaced. The keypad is then used to choose the proper remote unit for loading. Next, the LCD prompts the user to enter the new ID number for the remote unit, using the keypad. When this is complete, the microcontroller saves the ID number in a module and the LCD goes back to displaying the main menu. The remote unit is not used during this mode of operation. Figure 11 shows the software flow chart for the Load Mode.

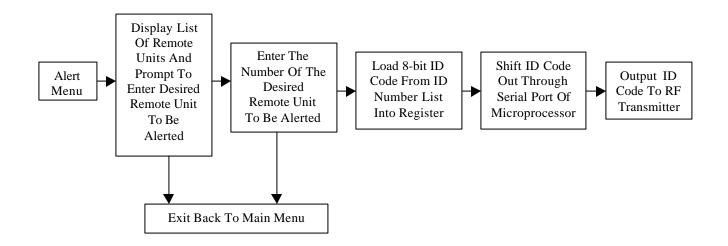

- Alert Mode: The LCD prompts the user to choose which remote unit is to be found. The keypad is used to scroll through the list and choose the name of the desired item to be located. The microcontroller repeatedly sends the saved ID number to the RF transmitter for a preset number of times. The remote ID number is then transmitted to each remote unit receiver. The receiver then demodulates the received signal and outputs the signal to the decoding circuitry. The decoding circuitry determines the ID number and compares it to the preset number of each remote unit. The remote unit that has the matching ID number produces the audible alert tone until the user turns it off on the base unit or the remote unit itself, using the alert off button. Figure 12 shows the software flow chart for the Alert Mode.

Figure 9 Software Flow Chart For The Main Menu

Figure 10 Software Flow Chart For The Save Mode

Figure 11 Software Flowchart For The Load Mode

Figure 12 Software Flowchart For Alert Mode

#### **Remote Units**

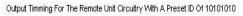

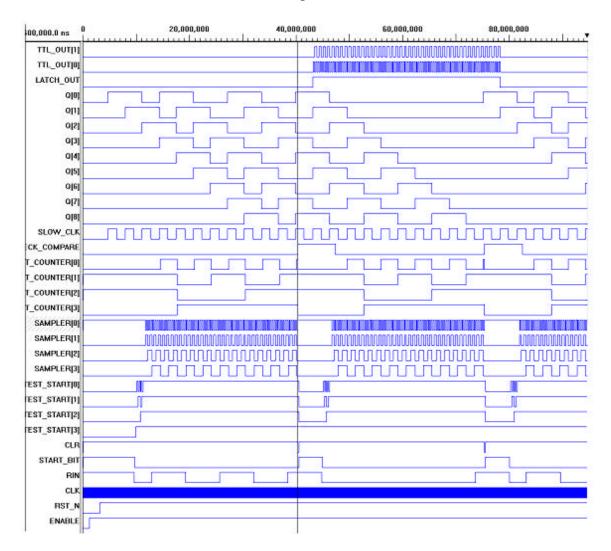

Figure 13 shows the functionality of the remote units. As soon as  $rst_n$  goes high the system becomes functional. The first action that takes place is the generation of  $slow_clk$ . This is generated using a frequency divider (counter) in the clock generation portion of the VHDL code shown in Appendix A-II. The counter divides clk four times, creating a 16 times slower clock called slow\_clk.  $Slow_clk$  is used for the shift register and compare circuitry, while clk is used for all other subsystems.

The next part of the code is the start bit detection. This code waits for the input, *rin*, to drop low and then the signal *start\_bit* is latched low. At this point the UART circuitry begins to sample at sixteen times the rate of *rin*. The UART signal, *test\_start*, then counts eight times from a negative transition in order to reach half the length of an input pulse, where the UART then takes another sample. Beginning at 1000b, *test\_start* counts up to 1111b. At this point, the UART checks to make sure that rin is still low. If *rin* is not low then the UART assumes the initial negative transition was due to noise in the transmission. The UART then resets the start bit latch and waits for the next *rin* negative transition. If it is low, then the UART assumes that this is the start bit.

At this point *sampler* begins to count all the way to 16 in order to obtain a sample halfway through each transmitted bit. Every time *sampler* reaches 16, *bit\_counter* increments. *Bit\_counter* is initially loaded to 0110b so that when it reaches 1111b, it will have counted nine bits (eight data bits and one stop bit). When *bit\_counter* reaches 1111b, the circuitry checks to make sure the last bit received, the stop bit, is a high bit. If the stop bit is not high, the system will reset and wait for the *rin* negative transition. If the stop bit is a high bit, *check\_compare* goes high.

When *check\_compare* is high, the UART circuitry acknowledges that all eight data bits have been received and the stop bit has been checked. When the values in the shift register match the values of the preset ID code, the compare output goes high. If the

compare output and *check\_compare* are high at the same time, meaning all bits have been checked counted and compare correctly, *latch\_out* goes high.

Latch\_out holds the output high until the user resets by pressing the appropriate alert tone off button. This circuitry is another frequency divider that divides clk by four, producing a 500Hz TTL output wave to the speaker. This wave is necessary in order to produce the desired tone from the speaker for alerting. At this point the system will wait for the user to press the tone off button on the remote. Otherwise, the remote unit will wait to receive a signal from the base unit stating that the user has pressed the button on the base unit. The signal needed to turn off the remote unit from the base unit is 000000001b. When the unit receives this from the base unit, the output latch will be reset and  $TTL_out[1]$  will stop. The system will then wait for the next transmission to occur, as shown in figure 13. The written VHDL code is shown in Appendix A-II.

Figure 13 VHDL Simulation Output Of The Remote Units

#### **Results**

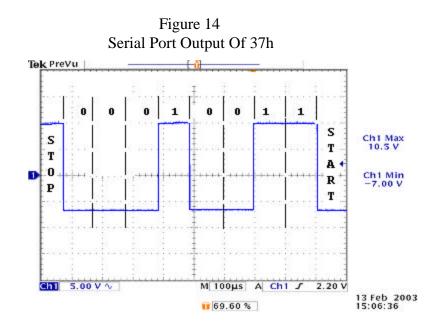

All components of this project that were implemented worked successfully. Due to time constraints, the save mode, load mode, and transceivers were not implemented. The base unit displayed the main menu and allowed the user to select the alert menu option. In this menu, the user has the ability to scroll through a list of saved items, select an item to be alerted, or go back to the main menu. When an item is selected, the EMAC inverts the ID code and then correctly packs it for transmission. Due to the ID code inversion, the preset values of the remote units will have to be inverted so that the compare circuitry will match the transmitted ID code. For example: if the ID code is 1111111b, the output of the serial port will be 00000000b. The output of the serial port for an ID code of 37h is shown in figure 14. The start bit is the low bit on the far right and the stop bit is the high bit on the left of the figure. Figure 14 shows how the onboard UART of the microcontroller inverts the signal. The actual signal is 00110111b (37h), but the serial port outputs 11001000b (C8h). For this reason, the preset ID code for this particular remote unit will be set to C8h.

The receiver successfully determines the start bit, eight data bits, and the stop bit of the transmitted packed serial bit stream. When the correct ID is sent, the corresponding remote unit produces the audible alert tone until the tone off button is pressed on the remote unit. At this time, all other remote units remain silent.

#### **Conclusions**

A necessary improvement for the actual production of this product is a power saving mode for the remote units. This would be advantageous to the owner of the product because it would increase the battery life of the remote unit. A second improvement would be to implement the remote unit with a microprocessor. The microprocessor would have code that would perform all of the VHDL functionality, in addition to having its own embedded transmission modules, eliminating the need for manually entering ID codes into the base station. A final improvement for the production of this product would be finding cheaper transceiver chips, LED screens, and keypads so that the price of the system would be less.

### Appendix A Software

#### I. Assembly Code For The Base Unit

#### Module #1: Setup

; The following "\$" commands must be included in every module SNOMOD51 ; Omit assembler predefined registers. \$INCLUDE(reg515.inc) ; Include 515/535 microcontroller definitions. NAME SETUP ; Optional parameter; if no name is provided, ; the filename will be used by default. EXTRN CODE (MAIN\_LOOP, SERINIT) EXTRN CODE (LCDINIT, KPD) ; Makes subroutine MAIN\_LOOP in the ; main.a51 module available to module ; setup.a51 . ST\_ADDR equ 8000h ; Set program starting address at 8000h. CSEG AT ST\_ADDR ; Places beginning of code at in a fixed memory ; location specified by ST\_ADDR = 8000h. ; This is referred to as an ; "absolute code segment", and cannot be relocated. BEGIN: LJMP START ; Jump to start of program. ST\_SEG SEGMENT CODE ; Reserve RAM space for 80535 initialization ; code segment, ST\_SEG. Again, since this is a ; "generic segment", it is relocatable. RSEG ST\_SEG ; Places the code segement containing ; START at this point in assembled code. ; The selected segment remains "active" until ; a different segment is specified. USING 0 ; Indicates to the assembler that register ; bank 0 will be used, but does not ; actually select register bank 0. ; Place code for initializations specific to the fundamental operation of the ; EMAC MicroPac 80535 microcontroller board here. START: CLR PSW.4 ; Selects register bank 0. CLR PSW.3 ; PSW bits 3 and 4 dictate register bank. MOV SP,#60h ; Initialize stack pointer to 60h. Note that ; the stack pointer could be initialized ; to any value between 20h and 7Fh. However, the programmer must ; ensure (1) stack has enough space to expand adequately, and ; (2) does not overwrite user data. MOV IEN0,#0 ; Disable all interrupts. P5.5 SETB ; Activates the external reset line. CLR P5.5 ; De-activates the external reset line. ; Make A16 of 128K RAM; system can use only SETB P5.0 ; the high 128K of the RAM space.

|        |              |                                       | ; Note that A16 MUST BE SET, with no exceptions.                                                                                                                   |

|--------|--------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | CLR          | P5.2                                  | ; Disable EEPROM by setting the EEPROM ; clock to its low level.                                                                                                   |

|        | CLR          | P5.1                                  | ; Enable memory mapped input/output (MMIO)<br>; to enable the keypad and LCD panel.                                                                                |

|        |              | itialization code<br>serial port, A/D | here specific to the operation of interrupts, , etc                                                                                                                |

|        | SETB         | EAL                                   | ; Enable all interrupts                                                                                                                                            |

|        | CALL<br>CALL | SERINIT<br>LCDINIT                    | · initialize ICD display                                                                                                                                           |

|        | CALL         |                                       | <pre>; initialize LCD display ; this is possible because subroutine LCDINIT ; has been made public and has been defined ; as external code in module lcd.a51</pre> |

|        | ;CALL        | KPD                                   |                                                                                                                                                                    |

|        | MOV          | R0,#2Fh ;                             | Clear a block of RAM (for example only).                                                                                                                           |

| CLR RA | м:           |                                       |                                                                                                                                                                    |

|        | MOV          | @R0,#0                                |                                                                                                                                                                    |

|        | DEC          | R0                                    |                                                                                                                                                                    |

|        | CJNE         | R0,#1Fh,CLR_RAM                       |                                                                                                                                                                    |

|        |              |                                       |                                                                                                                                                                    |

|        | LJMP         | _                                     | Transfer control to MAIN_LOOP code in module main.a51.                                                                                                             |

|        |              |                                       |                                                                                                                                                                    |

#### END

#### Module #2: Main

| ; main.a51 (Module #2)<br>;<br>; The following "\$" commands | must be included in every module                                                                                                                                                        |

|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>\$NOMOD51 \$INCLUDE(reg515.inc)</pre>                   | ; Omit assembler predefined registers.<br>; Include 515/535 microcontroller definitions.                                                                                                |

| NAME MAIN                                                    | ; Optional parameter; if no name is provided,<br>; the filename will be used by default.                                                                                                |

| PUBLIC MAIN_LOOP                                             | ; Lets other modules access this section of code<br>; from "public domain" utilizing the EXTRN command.                                                                                 |

| EXTRN CODE (LCDOUT, DISPM<br>;EXTRN CODE (LOAD, SAVE)        | ENU, KPD, ALERT, ALERTMENU)<br>; Makes subroutines LCDINIT and LCDOUT in the<br>; lcd.a51 module available to module main.a51 .                                                         |

| ;********                                                    | ******************                                                                                                                                                                      |

| MAIN SEGMENT CODE                                            | ; Reserve RAM space for the generic code<br>; segment, MAIN. The name segment name is referred<br>; to by the following RSEG directive.                                                 |

| RSEG MAIN                                                    | <pre>; Selects the MAIN code segement, and makes it ; "active" at this point in assembled code. ; The selected segment remains "active" until ; a different segment is specified.</pre> |

| USING 0                                                      | ; Indicates to the assembler that register<br>; bank 0 will be used, but does not actually<br>; select register bank 0 .                                                                |

| · The module main a51 should                                 | be used primarily to call subroutines in the                                                                                                                                            |

; The module main.a51 should be used primarily to call subroutines in the ; various modules in the project, as opposed to incorporating detailed functions ; within module main.a51 (i.e., main.a51 should be relatively short).

MAIN\_LOOP: CALL DISPMENU CALL KPD CJNE A,#31h,SV ;ALERT CALL ALERTMENU sv: CJNE A,#32h,LD ;CALL SAVE LD: ;CALL LOAD ; The call to LCDOUT is possible because ; subroutine LCDOUT has been made public, and ;CALL LCDOUT ; has been defined as external code in ; module lcd.a51 . LOOP: ; Infinite loop. JMP LOOP END

### Module #3: LCD Output Code

| \$NOMOD51<br>\$Include(reg                                                                                                | 515.inc)             | ; omit assembler micro definitions<br>; define 515 micro  |

|---------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------------------------------------------------|

| Name LCD                                                                                                                  |                      |                                                           |

|                                                                                                                           |                      |                                                           |

| LCD_DRV SEGM                                                                                                              | ENT CODE             |                                                           |

| RSEG                                                                                                                      | LCD_DRV              | ; switch to this code segment                             |

|                                                                                                                           | USING 0              | ; use register_bank 0                                     |

| <pre>\$Include(reg515.inc) ; define 515 micro Name LCD PUBLIC LCDOUT, LCDINIT EXTRN CODE (KPD) LCD_DRV SEGMENT CODE</pre> |                      |                                                           |

| ; definition                                                                                                              | S                    |                                                           |

|                                                                                                                           | psw.5<br>equ 28h     | ; LCD equate<br>; value for P2 to select lcd command port |

| initdata:                                                                                                                 |                      |                                                           |

| db                                                                                                                        | 38h,08,01,06,0eh,    | 80h,0                                                     |

| LCDOUT:                                                                                                                   |                      |                                                           |

|                                                                                                                           | R2,A<br>R2 #LCDCMD   |                                                           |

| jnb                                                                                                                       | ESCIlag, lcdnt5      |                                                           |

|                                                                                                                           |                      | ; write directly to lcd reg 0                             |

| lcdnt5:                                                                                                                   |                      |                                                           |

|                                                                                                                           |                      |                                                           |

|                                                                                                                           |                      |                                                           |

| ANL                                                                                                                       | A,#11111000B         |                                                           |

| MOV<br>CJNE                                                                                                               | A,R2<br>A,#0DH,LCNT1 | ; SEE IF CONTROL CHAR<br>; IF NOT CR, SKIP                |

|              | SETB<br>ANL<br>MOV                                            | ACC.7<br>A,#11100000B                                      | ; READ COMMAND FORT TO FIND CURSOR POS<br>; SET BIT 7 FOR DDRAM ADDR<br>; MOVE TO LEFT (ONLY VALID ON 2 LINE DISPL)                                          |

|--------------|---------------------------------------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LCNT1:       | MOVX<br>CPL<br>SETB<br>MOV                                    | A,@R1<br>ACC.6                                             | ; IF NOT LF, SKIP<br>; READ COMMAND PORT TO FIND CURSOR POS<br>; SWITCH LINE (ONLY VALID ON 2 LINE DISPL)<br>; SET BIT 7 FOR DDRAM ADDR                      |

| LCNT2:       | CJNE                                                          | A,#1BH,LCNT3<br>ESCflag<br>LCDEXIT                         | ; IF NOT ESC, SKIP<br>; indicate ESC received                                                                                                                |

| LCNT3:       | CJNE<br>MOV                                                   | REGOOUT                                                    | ; EXIT IF NOT CLEAR SCREEN<br>; CLEAR COMMAND<br>; OUTPUT THE CHAR IN R2 TO REG 1                                                                            |

| REG1OUT      | MOVX<br>JB<br>INC<br>MOV                                      | ACC.7,REG1OUT<br>P2<br>A,R2                                | ; READ LCD COMMAND PORT<br>; LOOP IF BUSY FLAG SET<br>; POINT TO LCD DATA PORT<br>; RESTORE CHAR<br>; OUTPUT IT                                              |

| LCNT4:       |                                                               |                                                            |                                                                                                                                                              |

|              | JMP I                                                         | LCDEXIT                                                    |                                                                                                                                                              |

| REG00U1      | r:                                                            |                                                            | ; OUTPUT THE CHAR IN R2 TO REG 0                                                                                                                             |

|              | MOV<br>MOVX                                                   | ACC.7,REG0OUT<br>A,R2                                      | ; READ LCD COMMAND PORT<br>; LOOP IF BUSY FLAG SET<br>; RESTORE CHAR<br>; OUTPUT IT                                                                          |

|              | NIT: Ini                                                      | t the LCD                                                  |                                                                                                                                                              |

| ;<br>LCDINIT | C:                                                            |                                                            |                                                                                                                                                              |

|              | clr<br>MOV<br>LCALL<br>LCALL<br>LCALL<br>LCALL<br>MOV<br>MOVX | P2, #LCDCMD<br>DLAYA<br>DLAYA<br>DLAYA<br>DLAYA<br>A, #30H | <pre>; indicate no esc found<br/>; POINT TO COMMAND PORT<br/>; 5MS DELAY<br/>; 5MS DELAY<br/>; 5MS DELAY<br/>; 5MS DELAY<br/>; 0UT TO LCD COMMAND PORT</pre> |

|              | LCALL<br>MOVX                                                 | DLAYA<br>@R1,A<br>DLAYA                                    | ; 5MS DELAY<br>; OUT TO LCD COMMAND PORT<br>; 5MS DELAY<br>; OUT TO LCD COMMAND PORT                                                                         |

|              | MOV                                                           |                                                            | ; POINT TO INIT DATA<br>; the last command should take no more than 40 uS.                                                                                   |

|              | mov                                                           | b,#80                                                      | ; for timeout of 80*3 * (12/clock)                                                                                                                           |

| LCDINI       |                                                               | ⊃ @ <b>∽</b> 1                                             | · read lad gommand part                                                                                                                                      |

|              | jnb                                                           | acc.7,LCDINIT1                                             | <pre>; read lcd command port ; exit if not busy ; loop till timeout ; exit if timeout</pre>                                                                  |

```

LCDINIT1:

A,@R1

; READ LCD COMMAND PORT

MOVX

ACC.7, LCDINIT1 ; LOOP IF BUSY FLAG SET

JB

CLR

А

MOVC

A,@A+DPTR

; GET BYTE FROM INIT TABLE

; EXIT IF 0

; POINT TO NEXT BYTE

JZ

LCDEXIT

INC

DPTR

MOVX

@R1,A

; OUTPUT BYTE

LCDINIT1

; LOOP

SJMP

LCDEXIT:

RET

;

; MISCELLANEOUS DELAYS added to keep the LCD from scrolling

; when the buttons are held down

DLAYA:

PUSH

ACC

A,#100

MOV

AJMP

DLAYA2

DLAYB:

PUSH

ACC

A,#128

MOV

AJMP

DLAYA2

DLAYC:

ACC

PUSH

MOV

A,#255

AJMP

DLAYA2

dlayd:

PUSH

ACC

MOV

A,#8

DLAYA2:

PUSH

ACC

MOV

A,#0FFH

DLAYA1:

MOV

A,#OFFH

; LEVEL 3 LOOP

DJNZ

ACC,$

POP

ACC

DJNZ

ACC, DLAYA2

; LEVEL 1 LOOP

POP

ACC

RET

```

#### Module #4: Main Menu

END

;The following "\$" commands must be included in every module

| \$NOMOD51<br>\$INCLUDE(reg515.inc) | ; Omit assembler predefined registers.<br>; Include 515/535 microcontroller definitions.                |

|------------------------------------|---------------------------------------------------------------------------------------------------------|

| NAME TOPMENU                       | ; Optional parameter; if no name is provided,<br>; the filename will be used by default.                |

| PUBLIC DISPMENU                    | ; Lets other modules access this section of code<br>; from "public domain" utilizing the EXTRN command. |

|                                    | ; Makes subroutines LCDINIT and LCDOUT in the                                                           |

; lcd.a51 module available to module main.a51.

| EXTRN CODE         | E (LCDOUT)   |                                                                                                                                                                                                                        |

|--------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| •************<br>' | *****        | ***********                                                                                                                                                                                                            |

| TOPMENU S          | SEGMENT CODE | ; Reserve RAM space for the generic code<br>; segment, TOPMENU. The name segment name is referred<br>; to by the following RSEG directive.                                                                             |

| RSEG 1             | FOPMENU      | <ul><li>; Selects the MAIN code segement, and makes it</li><li>; "active" at this point in assembled code.</li><li>; The selected segment remains "active" until</li><li>; a different segment is specified.</li></ul> |

| USING (            | 0            | ; Indicates to the assembler that register<br>; bank 0 will be used, but does not actually<br>; select register bank 0.                                                                                                |

; The module main.a51 should be used primarily to call subroutines in the

; various modules in the project, as opposed to incorporating detailed functions ; within module main.a51 (i.e., main.a51 should be relatively short).

#### DISPMENU:

;PUT MAIN MENU CODE HERE FOR DISPLAYING ALERT, SAVE, LOAD

DPTR,#LINE1 MOV ; initialize pointer

#### DISPLOOP:

|                  | CLR<br>MOVC<br>JZ<br>CALL<br>INC<br>SJMP | A<br>A,@A+DPTR<br>NEXTLINE<br>LCDOUT<br>DPTR<br>DISPLOOP |          |     |

|------------------|------------------------------------------|----------------------------------------------------------|----------|-----|

| LOOPEXI          | T:<br>RET                                |                                                          |          |     |

| NEXTLIN          | IE:<br>MOV<br>SJMP                       | DPTR,#LINE2<br>DISPLOOP                                  |          |     |

| LINE1:<br>LINE2: | db<br>RET                                | "(1) Alert (2) Save                                      | (3) Load | ",0 |

END

#### Module #5: Keypad Code

```

; KEYPAD subroutine: waits for key pressed and returns it in ACC.

; (MODULE #5)

;

$NOMOD51

; omit assembler micro definitions

$Include(reg515.inc)

; define 515 micro

Name

KEYPAD

PUBLIC KPD

EXTRN CODE (LCDOUT)

KEYPAD SEGMENT CODE

```

```

RSEG KEYPAD

; switch to this code segment

USING 0

; use register_bank 0

; Dempsey Note:

; This code was provided by EMAC

; It is not an efficient way to use keypad

; Normally must do other main code processing

; local definitions

KEYSEL EQU

38H

; KEYPAD PORT

KPD:

IE1, KPD ; LOOP TILL KEY PRESSED

JNB

CLR

; clear for next transition

TE1

PUSH

DPH

; SAVE DPTR

PUSH

DPL

DPTR, #KEYTABL ; POINT TO TRANSLATE TABLE

MOV

P2,#KEYSEL ; POINT TO KEYPAD PORT

A,@R1 ; GET KEY FROM PORT

MOV

MOVX A,@R1

A,#00011111B ; ONLY 5 BITS

ANL

MOVC

A,@A+DPTR ; TRANSLATE TO KEY FROM TABLE (ASCII)

POP

DPL

POP

DPH

RET

KEYTABL: DB '123C456D789EA0BF'

```

```

END

```

#### Module #6: Alert Mode Code

```

; ALERT MENU (MODULE #6)

$NOMOD51

; omit assembler micro definitions

$Include(reg515.inc)

; define 515 micro

Name ALERT_MENU

PUBLIC ALERTMENU

EXTRN CODE (KPD,LCDOUT,ALERT,LCDINIT,MAIN_LOOP)

ALRT SEGMENT CODE

RSEG ALRT ; switch to this code segment

USING 0

; use register_bank 0

*****

ALERTMENU:

MOV A,#1AH ;CLEARS LCD SCREEN

CALL LCDOUT ;

MOV

в,#4

CLR

А

DPTR, #ASCII ; MOVES DATA TABLE INTO DPTR

MOV

MOVC A,@A+DPTR ;MOVES DPTR INTO ACC

MOV R0,#15 ;MOVES 15 INTO REGISTER 0

R0,#15

ALERTMENU2:

LOOPEXIT

JZ

CALL LCDOUT

```

INC DPTR ; INCREMENTS THE MEMORY LOCATION IN DPTR TO ;THE NEXT LETTER TO DISPLAY MOVX A,@DPTR ALERT LOOP: DJNZ R0,ALERTMENU2 ;LOOPS UNTIL R0 IS 0 IN ORDER TO DISPLAY ALL THE ;TEXT SAVED IN ACC MOV @R1,A ;STORE ID# IN R0 CALL KPD DJNZ B,KPD\_LOOP ;WHEN THE LAST ITEM IS REACHED (B=0) A,#45H,RETURN ;DOUBLE CHECK KEYPAD FOR E BEFORE DISPLAYING CJINE ;EACH ITEM AGAIN ;OTHERWISE WAIT FOR KEY SJMP ENTER RETURN: ; DOUBLE CHECKS THE KEYPAD BEFORE RETURNING CJNE A, #42H, ALERTMENU ; TO THE TOP OF THE LIST (B = BACK TO MAIN MENU) SJMP BACK ;WAIT FOR KEYPAD ENTRY, ENTER OR NEXT ITEM ; IF ENTER: ADD 1 TO A (PUSH A FIRST TO REOPEN SAVED VALUE) ; IF NEXT: ADD 2 TO A TO MOVE ONTO THE NEXT ITEM NAME KPD\_LOOP: CJNE A, #42H, COMMANDS ;B = BACK TO MAIN MENU SJMP BACK BACK: ; IF B IS PRESSED, THE LCD WILL A,#1AH ;CLEAR THE SCREEN AND MOV CALL LCDOUT ; JMP MAIN\_LOOP ; DISPLAY THE MAIN MENU AGAIN COMMANDS: CJINE A, #46H, ENTER ; F = NEXT SJMP NEXT ENTER: CJNE A,#45H,WAIT ;E = ENTER MOV A,#0AH ;SKIPS TO THE NEXT LINE ON THE LCD CALL LCDOUT ; MOVES "TRANSMITTING..." INTO DPTR MOV DPTR, #TRANS MOV A,#ODH ; MOVES CURSOR TO BEGINNING OF LINE 2 LCDOUT CALL TRANSMITTING: ;THIS CODE DISPLAYS "Transmitting..." ;UNDER THE ITEM NAME WHEN THE ALERT CLR ;BUTTON IS PRESSED Α A,@A+DPTR MOVC TRANSEXIT JΖ LCDOUT CALL INC DPTR CALL TRANSMITTING ;LOOP UNTIL ALL LETTERS ARE DISPLAYED CALL ALERT MOV A,#1AH ;CLEAR LCD CALL LCDOUT ; ;AFTER TRANSMISSION, THE LCD WILL JMP MAIN\_LOOP ; DIPLAY THE MAIN MENU AGAIN TRANSEXIT: RET

NEXT:

```

CLEARS LCD FOR NEXT

MOV

A,#1AH

CALL

LCDOUT

;ITEM TO BE DISPLAYED

INC

DPTR

; MOVES THE DPTR TO THE NEXT LINE ON THE ASCII

; TABLE

MOVX

A,@DPTR

;STORES THE NEXT LINE IN ACC

MOV

R0,#15

JNZ

ALERTMENU2

SJMP

ALERTMENU

WAIT:

CALL

KPD

KPD_LOOP

JMP

LOOPEXIT:

RET

ASCII:

; PUT ASCII TABLE HERE

;first item name(in ASCII),ID#

; DB

;second item

;db

; PHONE

db 52h,45h,4Dh,4Fh,54h,45h,20h,20h,20h,20h,20h,20h,20h,20h,20h,55h

; REMOTE

;KEYS

HEAD

TRANS:

DB

"Transmitting....",0

;Displays "Transmitting...." when alert

;button is pressed

```

```

END

```

#### Module #7: Serial Port Output Code

| \$NOMOD5                           | 51                              | g "\$" commands<br>5.inc)       | <pre>must be included in every module ; Omit assembler predefined registers. ; Include 515/535 microcontroller definitions.</pre>                            |

|------------------------------------|---------------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                               | SERIAL                          |                                 | ; Optional parameter; if no name is provided,<br>; the filename will be used by default.                                                                     |

| PUBLIC                             | SERINI                          | T, SEROUT, ALEF                 | T; Lets other modules access this section of code ; from "public domain" utilizing the EXTRN command.                                                        |

| EXTRN                              | CODE                            | (LCDOUT)                        | ; Makes subroutines LCDINIT and LCDOUT in the<br>; lcd.a51 module available to module main.a51 .                                                             |

| MR1BDAT<br>MR2BDAT                 | ~                               | 00010011B<br>00000111B          | ;Set stop bit length = 1<br>;Put registers in memory spaces                                                                                                  |

| ACR                                | EQU 04H                         | ł                               | ;Auxiliary Control Register                                                                                                                                  |

| MR1B<br>SRB<br>CSRB<br>CRB<br>THRB | EQU<br>EQU<br>EQU<br>EQU<br>EQU | 08H<br>09H<br>09H<br>0AH<br>0BH | ;Mode Register B (1-receiver 2-transmitter)<br>;Channel B Status Register<br>;Clock Select Register B<br>;Channel A Command Register<br>;Tx holding register |

| ;************************************** |                           |                                   |                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|-----------------------------------------|---------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| SERIAL                                  | SEGMEN                    | T CODE                            | <pre>; Reserve RAM space for the generic code<br/>; segment, MAIN. The name segment name is referred<br/>; to by the following RSEG directive.</pre>                                                                                                                   |  |  |  |  |  |  |

| R                                       | RSEG                      | SERIAL                            | <pre>; Selects the MAIN code segement, and makes it<br/>; "active" at this point in assembled code.<br/>; The selected segment remains "active" until<br/>; a different segment is specified.</pre>                                                                    |  |  |  |  |  |  |

| U                                       | JSING                     | 0                                 | ; Indicates to the assembler that register<br>; bank 0 will be used, but does not actually<br>; select register bank 0 .                                                                                                                                               |  |  |  |  |  |  |

| SERINIT                                 | :                         |                                   |                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|                                         | MOV                       | A,#01010000B                      | ;Do from this command, down to 00010000                                                                                                                                                                                                                                |  |  |  |  |  |  |

| COM_B_R                                 | RESET:                    |                                   |                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|                                         | MOV<br>MOVX<br>ADD        | P2,#CRB<br>@R1,A<br>A,#-16        | <pre>;Subtracts 1 from the upper nibble; loop until = 0000<br/>;0101=Reset channel A interrupt<br/>;0100=Reset error status. Clears channel A received break,<br/>; parity error, and overrun error bits.<br/>;0011=Reset transmitter.<br/>;0010=Reset receiver.</pre> |  |  |  |  |  |  |

| COM_B_R                                 | JNZ<br>RESET.             | COM_B_RESET                       | ;0000=Reset MR pointer. Points MR pointer to MR1.<br>;0000=No command, exit loop.<br>;If the first 4 bits don't equal 0000 jump back to                                                                                                                                |  |  |  |  |  |  |

| COM_B_S                                 | SETUP:                    |                                   |                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|                                         | MOV<br>MOV<br>MOVX        | P2,#MR1B<br>A,#MR1BDAT<br>@R1,A   | ;Points Mode Register 1B to Port 2<br>;Initializes MR1B receiver first in order to<br>;initialize MR2B next for transmission.                                                                                                                                          |  |  |  |  |  |  |

|                                         | MOV<br>MOVX               | A,#MR2BDAT<br>@R1,A               | ;Stores mode register parameters in acc<br>;Move MR2BDAT into MR2B                                                                                                                                                                                                     |  |  |  |  |  |  |

|                                         | MOV<br>MOV<br>MOVX        |                                   | ;<br>;Points 80H into ACR in Port 2<br>;Baud Rate Generator Set Select = 1                                                                                                                                                                                             |  |  |  |  |  |  |

|                                         | MOV<br>MOV<br>MOVX        | P2,#CSRB<br>A,#01000100B<br>@R1,A | ;Set BAUD rate to 1.8kHz                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|                                         | MOV<br>MOV<br>MOVX<br>RET | P2,#CRB                           | ;Points data bits for CRB into Acc<br>;Points CRB into Port 2<br>;Points data bits into CRB at Port 2<br>;Enables the COM B - transmitter and reciever                                                                                                                 |  |  |  |  |  |  |

| ALERT:                                  |                           |                                   |                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|                                         | MOV                       | в,#20                             | ;WILL TRANSMIT THE NUMBER OF TIMES OF THE<br>;NUMBER STORED IN B                                                                                                                                                                                                       |  |  |  |  |  |  |

| SEROUT:                                 | :                         |                                   |                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|                                         | MOV<br>; POP<br>; MOV     | A,@R1<br>ACC<br>A,#37H            | ;PUTS THE ID# INTO THE ACC<br>;Test data to be sent to the transmitter                                                                                                                                                                                                 |  |  |  |  |  |  |

| JP | ACC    | 15012 | IDE . |    | TIAT | IO IN | - A |     |             |

|----|--------|-------|-------|----|------|-------|-----|-----|-------------|

| VC | А,#37Н | ;Test | data  | to | be   | sent  | to  | the | transmitter |

SEROUTB:

```

MOV

P2,#SRB

PUSH

ACC

; SAVE CHAR for later use

SOUTB1:

MOVX

A,@R1

;Point external Port 2 to Acc

ACC.2,SOUTB1

;Loop until SRB-bit 2 (TXrdy) is ready to transmit

JNB

POP

ACC

P2,#THRB

;Send out the serial bit stored

MOV

MOVX

@R1,A

DJNZ

B,SEROUT

RET

END

```

### II. VHDL Code For The Remote Unit

-- Re\_enable has been commented out because it is not a necessary signal for the code.

-- The purpose of re\_enable was to have a second reset so that rst\_n could be a main reset -- and re enable could be a user reset.

```

library IEEE;

use IEEE.std_logic_1164.all;

use ieee.numeric_std.all;

entity shftreg is

port

(

clk,rin,enable

: in std_logic;

: in std_logic;

rst_n

: out unsigned(1 downto 0)

TTL out

: buffer std_logic_vector(8 downto 0);

--Q

);

end shftreg;

architecture smy of shftreg is

signal IQ

: std_logic_vector(8 downto 0);

signal TTL_out_w

: unsigned(1 downto 0);

signal clk_w

: unsigned(3 downto 0);

signal sampler

: unsigned(3 downto 0);

signal test_start

: unsigned(3 downto 0);

signal bit counter

: unsigned(3 downto 0);

: std_logic;

signal latch_out

: std logic;

signal retest_start

signal sample

: std logic;

signal load

: std_logic;

signal inc

: std logic;

signal start_bit

: std_logic;

signal clr

: std_logic;

signal check_compare

: std_logic;

signal slow_clk

: std_logic;

```

```

-- Clock Generation Circuitry

```

```

process(rst_n,clk)

begin

if (rst_n = '0') then

clk_w <= (others => '0');

elsif rising_edge(clk) then

-- produces a 16 times slower clock for the

clk_w \leq clk_w + 1;

-- shift register, compare, TTL output code

end if;

end process;

slow_clk \ll clk_w(3);

-- Start Bit Detection

process(rst_n,clr,clk)

begin

if rst_n = '0' then

start_bit <= '1';</pre>

elsif rising_edge(clk) then

if (rin = '0') then

-- latches start_bit low when input drops low

start_bit \leq 0';

-- resets latch when clr = 0

elsif (clr = '0') then

start_bit <= '1';</pre>

elsif (re_enable = '0') then

__

start_bit <= '1';</pre>

__

end if;

end if;

end process;

-- UART Circuitry

process(clk, rst_n)

begin

if (rst_n = '0') then

test\_start \le (others \implies '0');

sampler <= "0001";

sample \leq 0';

load

<= '1';

<= '0';

inc

bit_counter <= "0110";

-- set bit_counter to 5 to count all 10 bits

check compare \leq 0';

clr <= '1';

retest_start <= '1';

elsif rising_edge(clk) then

clr <= '1';

if (re_enable ='0') then

---

test_start <= (others => '0');

---

sampler <= "0001";

--

sample \leq 0';

--

```

```

load

<= '1';

inc

<= '0':

bit counter \leq "0110";

check_compare <= '0';

clr <= '1':

retest_start <= '1';

end if;

if start_bit = '0' then

if (retest_start = '1') then

if (load = '1') then

test_start <= "1000";

load \leq 0';

elsif (test_start = "1111" and rin = '0') then

sample \leq 1';

retest_start <= '0';

elsif (test_start = "1111" and rin \neq '0') then

--RESET the start bit latch above

clr <= '0';

load <= '1';

else

test_start <= test_start + 1;</pre>

end if;

end if;

if (sample = '1') then

-- count 16 times then sample bit

sampler \leq sampler + 1;

end if:

if (\text{sampler} = "0100") then

-- limits check_compare clk period

check_compare <= '0';

end if;

if (\text{sampler} = "1111") then

-- counts 9 bits

bit_counter <= bit_counter + 1;</pre>

end if:

if (bit_counter = "1111" and rin = '1') then

-- all bits have been counted and

-- stop bit = 1

-- allows for comparing in shift

check_compare <= '1';

-- register

-- RESETS

clr <= '0':

-- resets the start-bit latch

load <= '1';

-- resets test_start

sample \leq 0';

-- stops sampler counting

retest_start <= '1';

-- activates the start-bit sampler

bit_counter <= "0110";

-- resets bit_counter

elsif (bit_counter = "1111" and rin /= '1') then

-- all bits have been counted

-- and stop-bit not = 1

-- RESETS

-- same resets as above

```

--

--

---

---

---

\_\_\_

\_\_\_

```

clr <= '0';

load <= '1':

sample <= '0';

bit_counter <= "0110";

retest_start <= '1';

end if:

end if;

end if:

end process;

-- Shift Register Circuitry

process(slow_clk,rst_n)

begin

if rst_n = '0' then

IQ \leq (others => '0');

elsif rising_edge(slow_clk) then

case enable is

when 0' => null;

when '1' \Rightarrow IQ \iff IQ(7 \text{ downto } 0) \& \text{ rin};

-- shifts the bits through

-- the register(MSB first)

when others => null;

end case;

if (re_enable = '0') then

IQ \leq (others => '0');

-- resets register if re_enable = 0

--

end if;

end if;

Q \le IQ;

end process;

-- Latch Circuitry\Compare Circuitry

process(rst_n,slow_clk)

begin

if rst_n = '0' then

latch_out \leq 0';

elsif rising_edge(slow_clk) then

if (re_enable = '0') then

latch_out <= '0';

-- resets latch if re_enable = 0

___

if (IQ = "000000001" and check_compare = '1') then

-- compares input to preset ID code

-- holds TTL output high until reset by user

latch out \leq 1';

elsif (IQ = "00000001" and check_compare = '1') then

latch_out <= '0';</pre>

--turns audible tone off when user presses

--button on the base unit

end if;

end if;

end process;

```

-- TTL Output Generation Circuitry

```

process(rst_n, TTL_out_w, clk) is

begin

if(rst_n = '0') then

TTL_out_w <= (others => '0');

elsif rising_edge(clk) then

if(latch_out = '1') then

TTL_out_w <= TTL_out_w + 1; -- creates TTL output wave to

end if; -- speaker for tone generation

end if;</pre>

```

end process;

TTL\_out <= TTL\_out\_w;

end smy;

## **Appendix B** Data Sheets and Pin Assignments

#### **Transceiver Data Sheet**

### PERFORMANCE DATA TR-XXX-SC

\*ABOUT THESE MEASUREMENTS The performance parameters listed below are based on module operation at 25°C from a 5VDC supply unless otherwise noted.

| TRANSMIT SECTION<br>Parameter | Designation  | Min        | Тур                 | Max    | Units      | Notes               |

|-------------------------------|--------------|------------|---------------------|--------|------------|---------------------|

| Center Frequency              | Fc           |            | SEE TABLE 1         |        | MHz        |                     |

| Fc Tolerance                  | 1.5          | -50        | Sale for Orseal ( ) | +50    | KHz        | 1                   |

| Output Power                  | Po           | -3         | -0                  | +4     | dBm        | 2,3                 |

| Output-Power Control Range    |              |            | 15                  | 12240  | Bb         | 24.8                |

| Harmonic Emissions            | Ph           |            | -43                 |        | dBc        | 199                 |

| Spurious Emissions            |              | le with FC | C part 15           |        | 1.222.0    |                     |

| Frequency Deviation           |              | 90         | 110                 | 130    | KHz        | 5                   |

| Data Rate                     |              | 300        | 3.53                | 33,600 | Bps        | 8                   |

| Aucio Modulation Bandwidth    | 8            | .15        | 1 1                 | 17     | KHz        | 7,8                 |

| Modulation Voltage            |              |            | 1 1                 |        | 14114      |                     |

| Digital (Mark)                |              | 3          | 5                   | 5.2    | VDC        | 9                   |

| Digital (Space)               |              | D          | a                   |        | VDC        |                     |

| Analog                        |              | ñ          | 100                 | 3      | Vp-p       | 10                  |

| RECEIVE SECTION               |              | , e        | <u> </u>            | ~      | •PP        | 10                  |

| LO Frequency                  | Flo          |            | SEE TABLE 1         |        | MHz        |                     |

| Flo Tolerance                 | 1.0          | -80        | OLL PADLE !         | +50    | KHz        |                     |

| Local Oscillator Feedthru     |              |            | -65                 | - 50   | dBm        | 2                   |

| Spurious Emissions            | compatib     | lo with Ef | C part 15           |        | GESTIN     | ÷                   |

| Receive Sensitivity           | company      | -90        | -94                 | -100   | dBm        | 6                   |

| Data Rate                     |              | 300        | -34                 | 33,600 | Bos        | 8                   |

| Required Transition Interval  |              | 300        | 1 1                 | 3.5    | ms         | 8.14                |

| Audio Bandwidth               |              | .15        | 1 1                 | 17     | KHz        | 7,8                 |

| Audio Lavel                   |              | . 10       | 180                 | 14     | mVp-p      | 8                   |

| RSSI DC Output Range          |              |            | 7 to 2.5            |        | w v        | 8                   |

| RSSIGain                      | Grasi        |            | 27                  |        | w<br>mV/dB | 8                   |

| RSSI Dynamic Range            | 431364       |            | 65                  |        | dB         | 8                   |

| ANTEN NA PORT                 |              | -          | 65                  |        |            | 0                   |

| Designed for match            |              | <u> </u>   | 50                  |        | ohms       | 8                   |

| TIMING                        |              |            | 55                  |        | unna       | 0                   |

| Power-on to Valid Receive     |              | -          | 6                   | 8      | mis        | 8.9.11              |

| Power-on to Valid Transmit    |              |            | 3                   | 5      | ms         | 8.9.11              |

| RX to Valid TX Switching      |              |            | 3                   | 5      | ms         | 8.9.12              |

| TX to Valid RX Switching      |              |            | 4                   | 8      | ms         | 8,9,13              |

| POWER SUPPLY                  |              | _          | -                   |        | me         | alotto              |

| Operating Voltage             | VCC (pin 10) | 2.7        |                     | 13     | VDC        |                     |

| Current Consumption           | loc          | 192        |                     | 1      |            |                     |

| TX Mode                       | The          | 12         |                     | 29     | mA         |                     |

| RX Mode                       |              | 10         | 13                  | 15     | mA         |                     |

| Sleep Mode                    |              |            | 50                  |        | UA.        | 8                   |

| ENVIRONMENTAL                 |              |            | 344 C               |        | - m        | ų.                  |

| Operational Temp.             |              | 0          | 1                   | 70     | °C         | <ul> <li></li></ul> |

| operational temp.             |              | U.         |                     | 10     | ~          |                     |

"Table applies to S/N >3000

### **Transceiver Pin Assignments**

### PIN DESCRIPTION

Figure 5: SC Series Pinonts (viewed looking down on top cover)

| PIN#             | PhTtle                                                | Description                                                          |  |  |

|------------------|-------------------------------------------------------|----------------------------------------------------------------------|--|--|

| 1,11,13<br>15-20 | Ground                                                | Module Grounds<br>Tie to Common Groundplane                          |  |  |

| 2                | RXDATA                                                | Recovered Data Output                                                |  |  |

| 3                | AUDIO                                                 | Recovered Analog Output                                              |  |  |

| 4                | RSSI                                                  | Received Signal<br>Strength Indicator                                |  |  |

| 5                | PDN                                                   | Logic Low Powers Down<br>The Transceiver                             |  |  |

| 6                | N/C                                                   | Not Implemented<br>Do Not Connect                                    |  |  |

| 7                | RXEN                                                  | Receiver Enable Pin<br>Active High<br>Pull Low When in TX            |  |  |

| 8                | TXEN                                                  | Transmitter Enable Pin<br>Active High<br>Puil Low When in RX         |  |  |

| 9                | TXDATA Analog or Digital Content<br>to be Transmitted |                                                                      |  |  |

| 10               | VIN 2.7-13VDC Supply                                  |                                                                      |  |  |

| 12               | ANT 500 Antenna Port<br>TX/RX Switch Inside Module    |                                                                      |  |  |

| 14               | LVLADJ                                                | Open for Maximum TX Power<br>Insert Resistor to Reduce by up to 15dB |  |  |

### **CPLD Pin Assignments**

#### 44-PIN PLCC CONNECTION DIAGRAM (M4(LV)-32/32 AND M4(LV)-64/32)

### **Product Data Sheet**

| Dimensions                 | LX                                | WXI      | Η          |            |  |  |

|----------------------------|-----------------------------------|----------|------------|------------|--|--|

| Base Unit:<br>Remote Unit  | 6" X 4" X 3"<br>.5" X .5" X .125" |          |            |            |  |  |

| Number of remote units: 8  |                                   |          |            |            |  |  |

| Power Supply               | Min                               | Тур      | Max        | Unit       |  |  |

| Operating Voltage          |                                   |          |            |            |  |  |

| Base Unit:<br>Remote Unit: | 7<br>2.7                          | 3.3      | 15<br>13   | Vdc<br>Vdc |  |  |

| Current Consumption        |                                   |          |            |            |  |  |

| Base Unit:<br>Remote Unit: | 10                                | 45<br>13 | 85<br>29   | mA<br>mA   |  |  |

| Power:                     |                                   |          |            |            |  |  |

| Base Unit:<br>Remote Unit: | .315<br>27                        | 43       | 1.3<br>377 | W<br>mW    |  |  |

| Operational Temp:          | 0                                 |          | 70         | °C         |  |  |

The values on this data sheet were estimated due to the fact that nothing has actually been built and tested in the lab yet. The dimensions for the base unit were based off of the dimensions of a Micro Pac 8051 microcontroller board and an LCD screen. The remote unit dimensions were based off another remote unit device that was found during a patent search. The power supply ratings were based off of the microcontroller board for the base unit and the receiver for the remote unit.

### Appendix C Product Manufacturing Pricing

#### Remote unit:

Processor: AT tiny 12L-4sc: 8-pin surface mount/ 4MHz/ in-system programmable ---- \$1.46 Receiver: RXM-433-LC-S-ND Surface mount 433MHz receiver ---- \$9.85 Speaker: P9902 TR-ND: 8.5mm x 8.5mm/ 92dB/ surface mount/ 2.5KHz→2.7KHz range ---- \$2.234 Custom-made Casing: Estimated at \$1.50 Antenna: part of board. Battery: P189-ND Panasonic CR2032: 3V/ 220mAh/ 20mm ---- \$0.21675 Battery Holder: BA2032 SM-Bulk-ND: Surface mount coin 20mm battery holder ---- \$0.35 Audible Alert Off Button: P8006S Momentary switch ---- \$0.099 PCB: \$.65 / sq in. = 1 x 1 in. = \$0.65

#### HCP = \$16.36 LCP = .1\*TPC = \$1.82 TPC = HCP/.9 = \$18.18

#### **Base Unit:**

Processor: ATMEL AT 90S1200-4YC --- \$2.05LCD: Vacuum fluorescent display/ 2x20 lines --- \$4.95Keypad: \$2.00Custom-made Casing: Estimated at: \$2.5 - \$3Transmitter: TXM-433-LC-ND surface mount 433MHz transmitter --- \$4.90Power Supply: Diamond 35-6-500D: 6V/ 500mA --- \$1.53/per unit Antenna: \$1PCB 2 x 2 in \* \$0.65 = \$2.60HCP = \$21.53LCP = .1\*TPC = \$2.39TPC = HCP/.9 = \$23.92

#### Total cost of package: \$96.64 (with 4 remote units)

This pice is very high due to the expensive transmitter, receiver, LCD, and keypad. If the product were actually produced by a major company, an ASIC chip with a transceiver built in would be used. This would lower the price of each remote and base unit \$10. A major company would also have better connections, so the LCD and keypad would be found at a much cheaper price. I estimate that the cost of the total product would be approximately \$60 cheaper if a major production company were building it.

### Appendix D Other Works

Patent Number WO0217265: